Researchers have presented analytical formulas for simplified but useful qubit geometries that predict surface dielectric loss when its thickness is much less than the metal thickness, the limiting case needed for real devices. These formulas can thus be used to precisely predict loss and optimize the qubit layout.

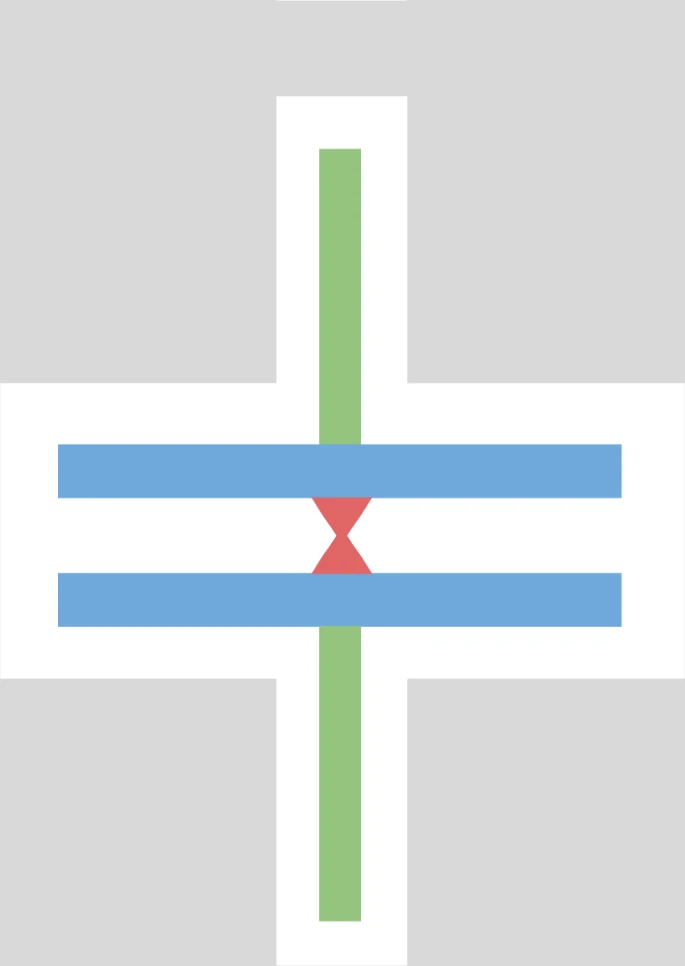

Surprisingly, a significant fraction of surface loss comes from the small wire that connects the Josephson junction to the qubit capacitor. Tapering this wire is shown to significantly lower its loss. Also predicted are the size and density of the two-level state (TLS) spectrum from individual surface dissipation sites.

Superconducting qubits can be thought of as an inductor-capacitor resonator, with the superconducting Josephson junction giving a non-linear inductance that allows the two lowest energy levels to behave as a qubit.

The Josephson junction and the capacitance are designed to be separate physical entities and thus can be separately optimized. The size of the Josephson junction is about 100 nm. Its natural capacitance is negligible and junction defects are statistically unlikely because of its small size; the junction can thus typically be modeled as bringing no energy loss. The capacitance is made from superconducting pads with a relatively large millimeter size and about 100 μm spacing, producing a capacitance of about 100 fF for the transmon qubit.

When the capacitor is designed properly with control lines weakly coupled to an external circuit, dielectric surface loss from the superconductor and substrate is the dominant mechanism of energy loss. As for any surface loss mechanism, it has been found experimentally that increasing the size of this capacitor lowers the net effect of the surface loss on the qubit device.

The paper has been published in npj Quantum Information.